FPGA HW tervezői verseny 2018

A hagyományoknak megfelelően a BME Méréstechnika és információs rendszerek tanszék idén is meghirdeti az FPGA HW tervezői versenyt.

A versenyre két fős csapatok jelentkezését várjuk. A csapattagoknak (aktív vagy passzív) BME hallgatói jogviszonnyal kell rendelkeznie és meg kellett kezdenie a BSc második évét (azaz bármilyen BSc és MSc hallgató jelentkezhet, kivéve a BSc első évfolyamát).

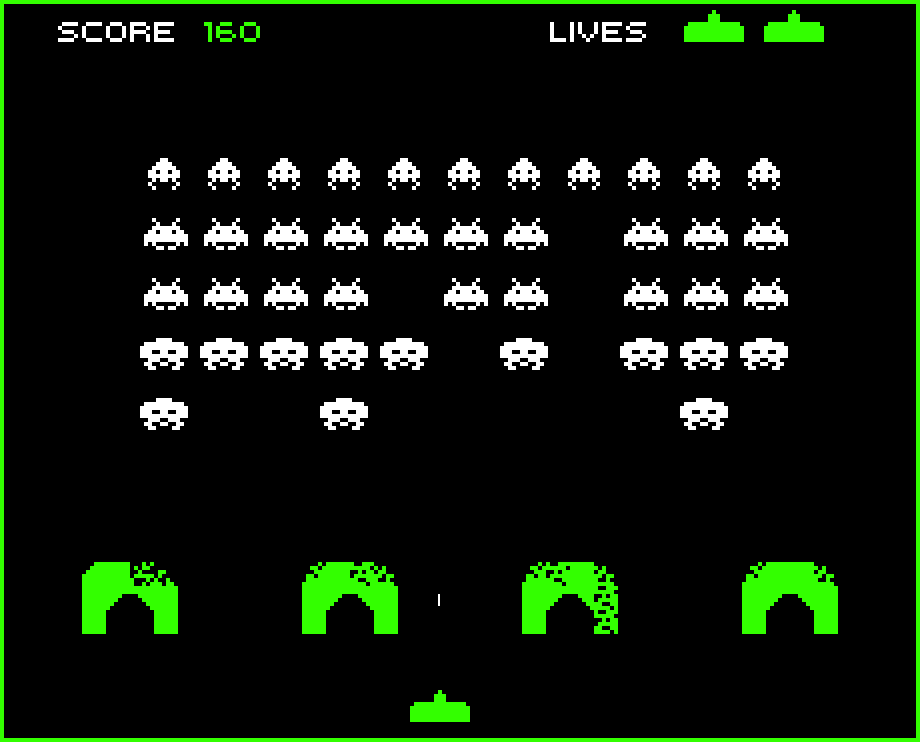

Az FPGA HW tervezői verseny témáját tekintve idén visszatérünk a játék-klasszikusokhoz, a feladat most a Space Invaders című játék megvalósítása.

A tervezési feladat

|

A feladat a több platformra megjelent Space Invaders játék megtervezése, közvetlen hardver megoldással (tehát nem használva szoft processzort az FPGA-ban a játékmenet futtatására) a LOGSYS Kintex 7 fejlesztői kártyán, felhasználva a HDMI és audió kimeneteket. A fejlesztéshez szükséges speciális HW eszközöket a pályázók számára a MIT tanszék biztosítja, a további esetlegesen szükséges komponensek (VGA monitor, PS/2 billentyűzet és/vagy egér) beszerzése a pályázók feladata. A tervezéshez szükséges Xilinx Vivado 2017.4 fejlesztési környezet letölthető a Xilinx cég honlapjáról. A Logsys Kintex 7 kártyához kiinduló projekt (HDMI adó) INNEN tölthető le.

A feladatkiírás részletei

A megvalósítás a https://en.wikipedia.org/wiki/Space_Invaders weboldal Gameplay fejezete szerint ismertetett játékszabályok szerint történjen, a könnyebb összehasonlíthatóság érdekében. Az alapvető cél az eredeti Taito-s verzió implementálása (https://www.youtube.com/watch?v=Sx0ZcT2fY0U), de természetesen a grafika tetszőleges mértékben javítható akár a PC-s verzió (https://www.youtube.com/watch?v=km3J6_Mvcg4) szintjére.

|

|

|

Általános jellemzők

A HDMI kimenet felbontása a szabványos értékek közül tetszőlegesen választható (legfeljebb 1600x900). A felhasználói kezelőfelület jellemzően billentyűzet, de lehet inkrementális jeladó, esetleg a fejlesztőkártya nyomógombjai. A játék tartalmazhat akusztikus visszajelzést, zenei hátteret.

A hardver terv tetszőleges formában elkészíthető, HDL, kapcsolási rajz, más magas szintű leírás. A pályázat tartalmazza a tervet megvalósító projekt rövid szöveges technikai dokumentációját, maximum 10 oldal terjedelemben és a megoldást ismertető 6 diából álló PPT bemutatót. A dokumentáció a rendszer blokkvázlatát, a fontosabb egységek rövid leírását és az értékelési kritériumnak megfelelő számszerű paramétereket tartalmazza. A diabemutató az előzetes értékelés alapján kiválasztott legjobb 5 pályázó munkájának bemutatásához szükséges.

Értékelési kritériumok

Az értékelés alapja a terv műszaki paraméterei (50%), játék használhatósága (30%), és a bemutató színvonala (20%). A terv műszaki paraméterei között a fontos kritérium a rendszertechnika logikus, szép felépítése, funkcionalitáshoz mért FPGA logikai erőforrásigények mértéke (LUT, FF, BRAM, stb.), de természetesen a grafika és a hangahtások kivitelezése is döntő szempont.

Díjazás

Az első három helyezett csapat mindkét tagját Xilinx FPGA alapú fejlesztői kártyával jutalmazzuk. A tervezett nyeremények a következők (még változhat!):

- 1. díj: Digilent Pynq fejlesztői kártya

- 2. díj: Digilent Zybo fejlesztői kártya

- 3. díj: Avnet MiniZED fejlesztői kártya

Döntő és eredményhirdetés: 2018. június 25.

Résztvevők

A versenyre két fős csapatok jelentkezését várjuk. A csapattagoknak (aktív vagy passzív) BME hallgatói jogviszonnyal kell rendelkeznie és meg kellett kezdenie a BSc második évét (azaz bármilyen BSc és MSc hallgató jelentkezhet, kivéve a BSc első évfolyamát).

Nevezés, fejlesztőeszközök igénylése:

- Dr. Fehér Béla egyetemi docens, feher@mit.bme.hu,

- Szántó Péter egyetemi mestertanár, szanto@mit.bme.hu

Nevezési határidő: 2018. május 17.