2017 - videofeldolgozás

FPGA HW tervezői verseny 2017

A hagyományoknak megfelelően a BME Méréstechnika és információs rendszerek tanszék idén is meghirdeti az FPGA HW tervezői versenyt.

A versenyre két fős csapatok jelentkezését várjuk. A csapattagoknak (aktív vagy passzív) BME hallgatói jogviszonnyal kell rendelkeznie és meg kellett kezdenie a BSc második évét (azaz bármilyen BSc és MSc hallgató jelentkezhet, kivéve a BSc első évfolyamát). Az elsős BSc hallgatóknak szóló feladat kiírás itt található.

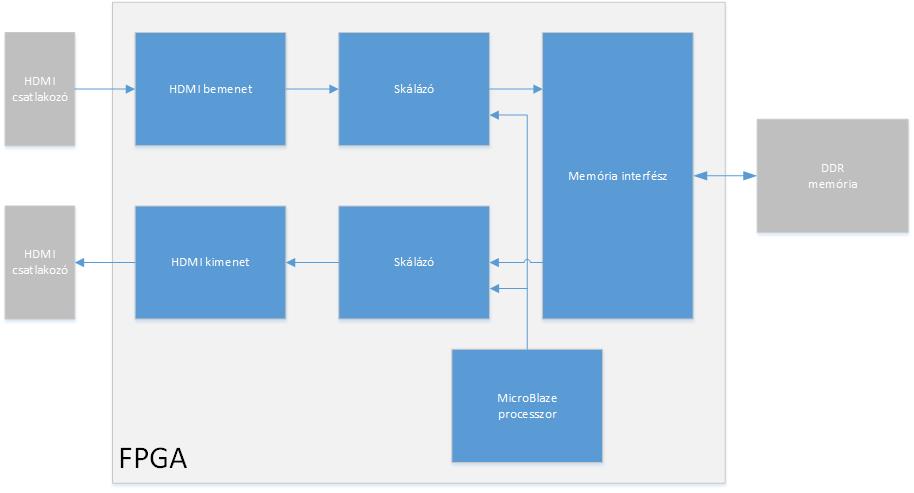

Az FPGA HW tervezői verseny témája 2017-ben videó átméretező egység (IP core) megvalósítása. A hasonló, skálázást megvalósító feldolgozó egységek szinte minden videó feldolgozásban használt feldolgozó láncban helyet kapnak, gondoljunk csak a különböző videó falakra, a video megjelenítésnél a kép-a-képben funkcióra, vagy a ROI (region of interest) típusú tartalom kiemelésre. A verseny során megvalósítandó, tisztán hardveres egységnek képesnek kell lennie tetszőleges felbontásról másik tetszőleges felbontásra átméretezni, de vezérlési funkciókra (pl. paraméter számítás) használható processzor is, valamint külső memória is rendelkezésre áll.

|

|

|

|

A tervezési feladat

A tervezési feladat egy hardveres videó skálázó egység megvalósítása, amely tetszőleges felbontású szabványos videó folyamból másik, tetszőleges felbontású videó folyamot képes előállítani. A ki- és bemeneti videófolyam jelei:

- pix_clk: pixel órajel.

- de: adat érvényes jel, ami mutatja, hogy az aktuális pixel a látható képtartományban van.

- hsync: horizontális szinkornjel.

- vsync: vertikális szinkronjel.

- rgb: 3x8 bites szín információ.

A videófolyam mellett tetszőleges számú vezérlő bemenet, illetve státusz kimenet használható. A vezérlő bemenetek értékeinek előállítása nem része a tervnek, ezeket számolhatja processzor, illetve a fix felbontású demonstrációs projektekben konstans vezérlés is megfelelő.

A megvalósított egységnek működnie kell szimulációban, illetve két demonstrációs konfigurációt is be kell mutatni (az skálázó blokk NEM használhatja ki, hogy a felbontások előre ismertek, a példányosíásnál a szükséges bemeneti paraméterek igen):

- leskálázás: 1280x720-ról 640x480 felbontásra

- felskálázás: 640x480 felbontásról 1280x720 felbontásra

A fejlesztéshez, illetve demonstrációhoz a Digilent Atlys-6 kártyáját javasoljuk használni, amely rendelkezik HDMI ki- és bemenetekkel. Ezt a jelentkezőknek a tanszék biztosítja (természetesen saját, tetszőleges típusú kártya is használható). Ezen kívül rendelkezésre áll egy, a HDMI ki- és bemeneteket megvalósító konfiguráció, melybe a megvalósítandó modul beilleszthető. A skálázáshoz használt algoritmus szsbadon megválasztható, a skálázás minősége része a bírálati szempontoknak. A legáltalánosabb (és ennek megfelelően a legbonyolultabb) megvalósítás blokkvázlata (a fenti demo konfigurációk ennél egyszerűbben is megvalósíthatók!):

A hardver terv tetszőleges formában elkészíthető, HDL, kapcsolási rajz, más magas szintű leírás. A pályázat tartalmazza a tervet megvalósító projekt rövid szöveges technikai dokumentációját, maximum 10 oldal terjedelemben, a megoldást ismertető 6 diából álló PPT bemutatót és a teljes projektet. A dokumentáció a rendszer blokkvázlatát, a fontosabb egységek rövid leírását és az értékelési kritériumnak megfelelő számszerű paramétereket tartalmazza. A diabemutató az előzetes értékelés alapján kiválasztott legjobb 5 pályázó munkájának bemutatásához szükséges.

Értékelési kritériumok

Az értékelés alapja a terv műszaki paraméterei (40%), a komplexitás és képminőség (40%), és a bemutató színvonala (20%). A terv műszaki paraméterei között a legfontosabb kritérium a rendszertechnika logikus, szép felépítése, illetve a funkcionalitáshoz mért FPGA logikai erőforrásigények mértéke (LUT, FF, BRAM, stb.).

Résztvevők

2 fős hallgatói csapatok a BME tetszőleges, de legalább Bsc 2. évfolyamáról, szakáról

Nevezés, fejlesztőeszközök igénylése:

- Dr. Fehér Béla egyetemi docens, feher@mit.bme.hu,

- Szántó Péter egyetemi tanársegéd, szanto@mit.bme.hu

Határidő, pályázat beadása

A pályázatokat 2017. június 18éjfélig kell beküldeni elektronikus formában, a nevezésnél megadott címre. Az előzetes értékelés alapján kiválasztott legjobb 5 pályaművet a nevező csapatok 2017. június 21-én mutathatják be a Méréstechnika és Információs Rendszerek Tanszék FPGA laboratóriumában, az I. épület IE321-es teremben. A PPT diák bemutatására 10-10 perc áll rendelkezésre, ezután a zsűri működés közben ellenőrzi a terveket. Eredményhirdetés 17 órakor, a zsűri rövid tanácskozása után.

Díjazás

A verseny díjazása:

- 1. díj: Digilent ZedBoard fejlesztői kártya

- 2. díj: Digilent Zybo fejlesztői kártya

- 3. díj: Digilent Pynq fejlesztői kártya

- Közönségdíj: Logsys Spartan-6 fejlesztői kártya

A verseny támogatói

|

|

|

|

Letöltések

- ISE 14.7 projket letöltése.

- A HDMI kábeleket a tápcsatlakozó oldalán levő HDMI In és HDMI Out csatlakozókba kell dugni, a JP6 és JP7 tüskéken pedig ne legyen jumper. Specifikáció szerint a FullHD felbontás már nem támogatott, de gond nélkül szokott menni. Esetleges probléma, kérdés esetén keressétek Szántó Pétert (IE336 szoba).