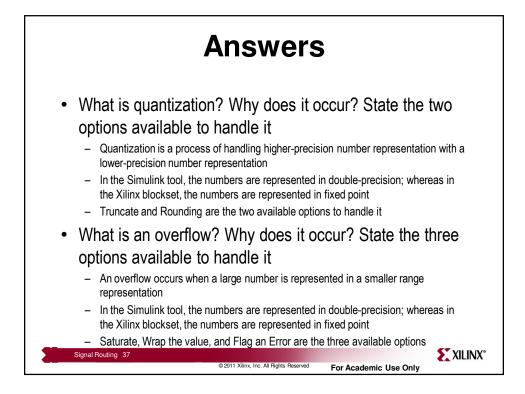

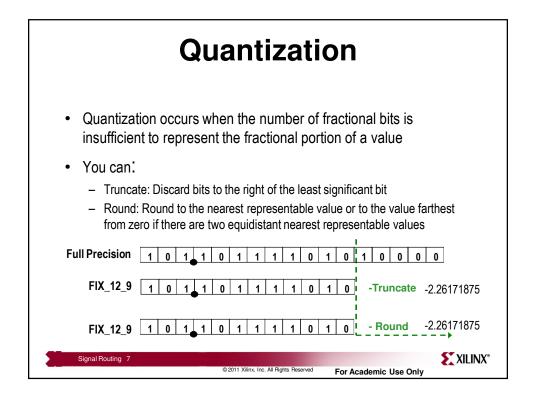

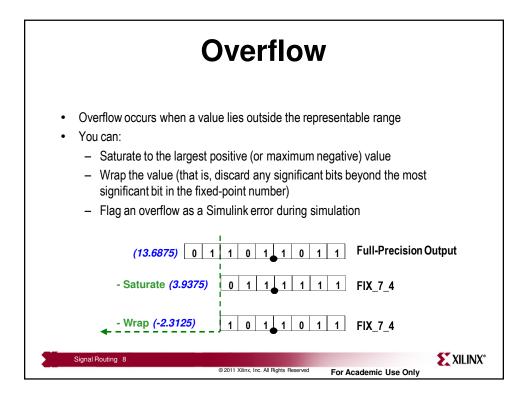

| Quantization and Overflow                                                                                                                                              |               |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

| 😂 Mult (Xilinx Multiplier)                                                                                                                                             |               |  |

| Hardware notes: To use the internal pipeline stage of the dedicated<br>multiplier you must select 'Pipeline for maximum performance'.<br>Basic Advanced Implementation |               |  |

| Precision:<br>Full User defined                                                                                                                                        |               |  |

| User Defined Precision<br>Output type:                                                                                                                                 |               |  |

| Number of bits     16       Binary point     14                                                                                                                        |               |  |

| Quantization:                                                                                                                                                          |               |  |

| Overflow:                                                                                                                                                              |               |  |

| Signal Routing 6 ©2011 Xilinx, Inc. All Rights Reserved For Academic Use Only                                                                                          | <b>XILINX</b> |  |

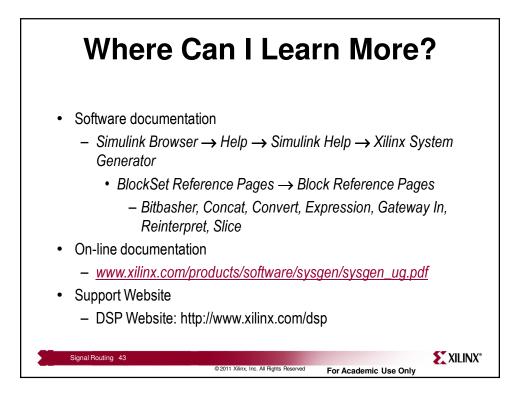

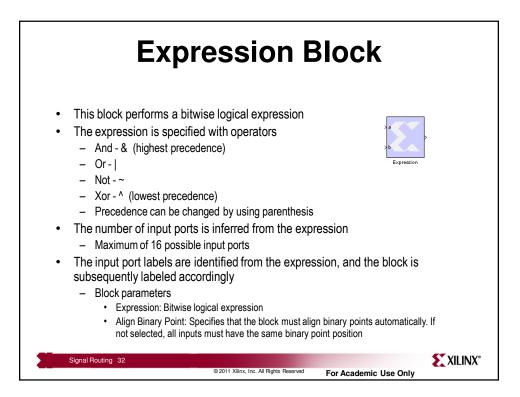

| Expression Block                                                                                                                                                                                                                        |                                                                                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| generate the resulting symbol<br>- ~((A1   A2) & (B1 ^ B2))                                                                                                                                                                             | the block parameters Expression field will                                                             |  |

| Expression (Xilinx Bitwise Expression Ev      Basic Output Type Advanced Implementation     Expression ("(A1   A2) & (B1 ^ B2)]     Align binary point     Optional Pots     Provide enable port     Latency 0     OK Cancel Help Apply | Expression (Xilinx Bitwise Expression Ev     Basic Output Type Advanced Implementation      Precision: |  |

| Signal Routing 33<br>© 2011 Xilinx, Inc. All Rights Reserved For Academic Use Only                                                                                                                                                      |                                                                                                        |  |